CoaXPress 主機 IP 核心

CoaXPress 主機 IP 核心用於 FPGA

- 相容於 AMD 7 系列(及更新版本)

- 相容於 Altera Cyclone 10 裝置(及更新版本)

- 體積緊湊

- 可自訂

- 支援 1 Gbps 至 100 Gbps 傳輸速率

- 以可運作參考設計形式交付

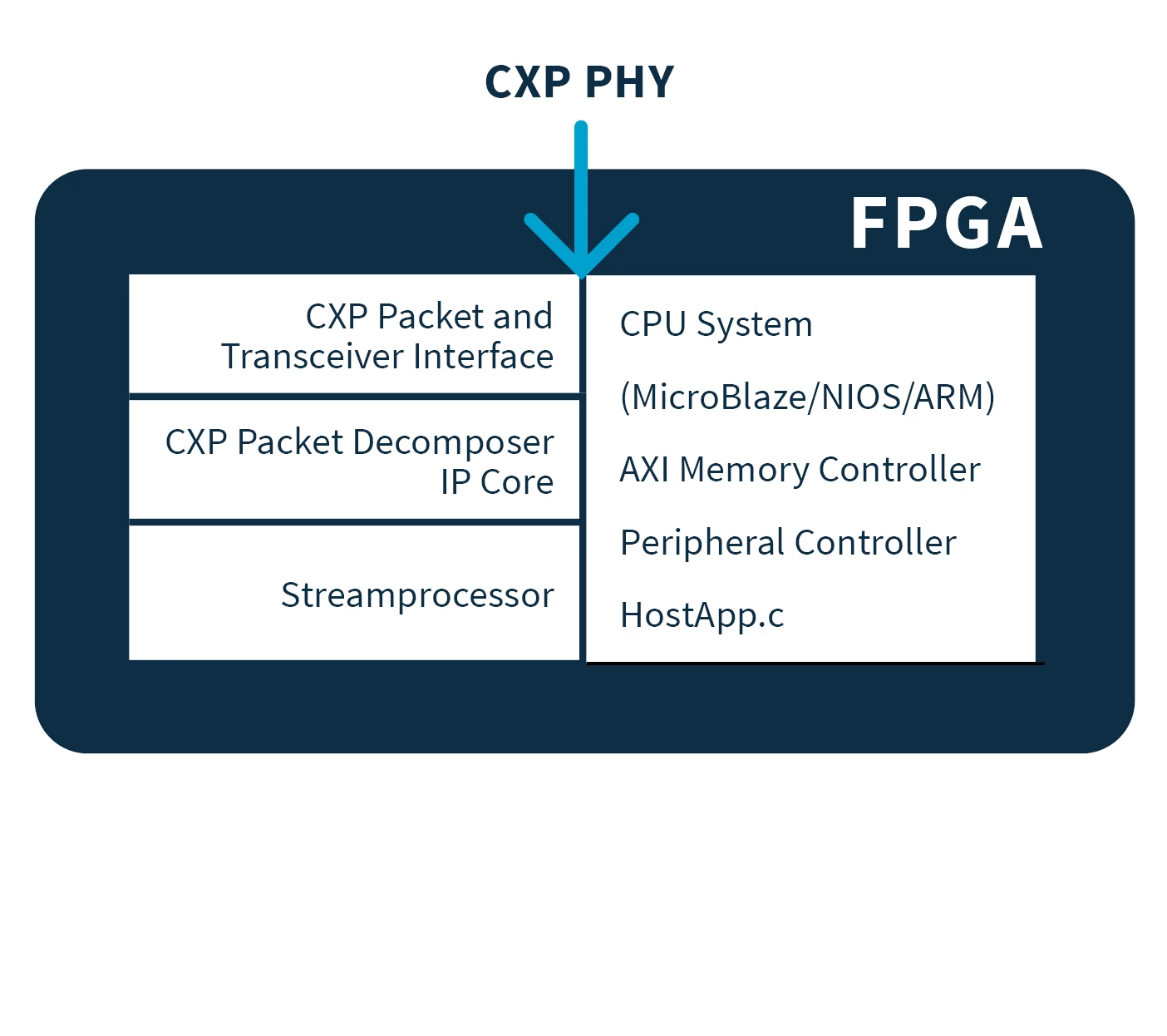

建築

CoaXPress(CXP)是一種基於廣泛使用的同軸電纜的視覺應用通訊標準協議。它能輕鬆實現相機與影像擷取卡或嵌入式處理器之間的介接,並支援GenICam軟體標準。 Sensor to Image 提供一組 IP 核心與開發框架,用於建構基於 CoaXPress 介面的 FPGA 接收器。鑑於 CXP 的高速特性,接收器需採用嵌入式收發器實現基於 FPGA 的高速 CXP 核心。CXP 主機核心相容於 AMD 與 Altera 裝置。

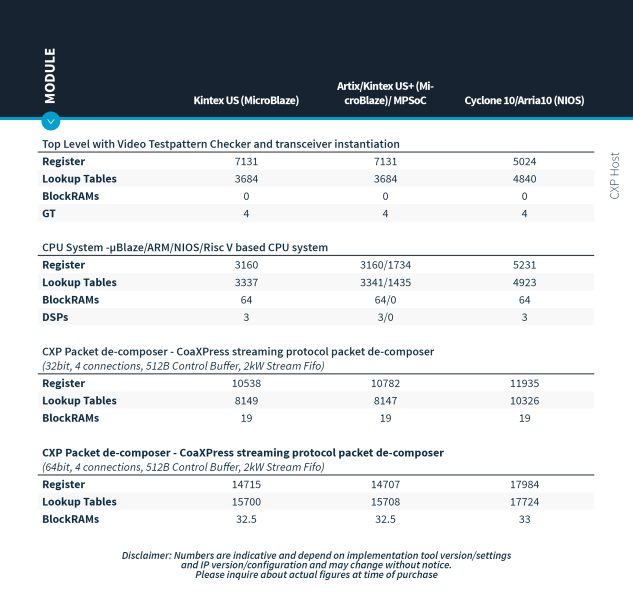

資源使用

下載資源使用情況效益

MVDK 機器視覺開發套件適用於 CoaXPress

Sensor to Image MVDK開發套件是一款適用於機器視覺應用的靈活評估平台。它支援CoaXPress主機與裝置參考設計,適用於搭載Altera與AMD FPGA的各類Enclustra FPGA模組。

光纖傳輸CoaXPress

另有獨立的CoaXPress-over-Fiber橋接器IP核心可用於光纖纜線,適用於更長距離、更高傳輸速率或更嚴苛的環境。

提供的參考設計

功能完備的參考設計:S2I 的 FPGA 解決方案以獨立運作的完整參考設計形式交付,該設計在經雙方確認的通用平台上運行,並整合 FPGA IP 核心。此設計能大幅縮短開發週期,在小巧體積下實現頂尖效能,同時保留足夠的設計彈性以供客製化調整。從感測器到影像的核心模組結構緊湊,為您的應用程式在 FPGA 中預留充足空間。

FPGA整合式CPU

採用FPGA整合式CPU(MicroBlaze、NIOS、ARM、Risc V)執行多項非時效性控制與配置任務,並與CXP裝置/主機核心協作。此軟體以C語言編寫,客戶可輕鬆進行擴充。

頂層設計

IP核心的第一個組件是頂層設計。它作為外部硬體(成像器、感測器、CXP物理層)與FPGA內部資料處理之間的介面。我們以VHDL原始碼形式交付此模組,可根據客製化硬體需求進行調整。

CXP封包分解器

CXP控制介面負責傳送與接收CXP控制通道的所有資料。外部CXP相機即透過此通道進行控制。CXP串流介面則解碼來自相機的所有資料,並以AXI串流形式輸出。此串流可用於後續處理。 CXP封包解構器與CXP傳輸層控制器進行通訊,該控制器實現了與FPGA收發器的高速介面。此IP核心提供32位元或64位元寬資料路徑,以實現最佳資源-效能比。64位元資料路徑使該IP核心具備CXP-25的相容性。

流處理模組

以視訊處理為例,參考設計配備簡易顯示單元或圖案檢測模組,用以展示CXP封包組態單元所產出的視訊串流輸出應用。

FMC介面擴充模組

為擴展各類參考板的功能,我們設計了提供額外介面的 FMC(FPGA 夾層卡)。我們提供適用於 Microchip 或 Macom 晶片組的 CXP-6 與 CXP-12 硬體相容板卡。